#### CPE 487: Digital System Design Spring 2018

# Lecture 12 VHDL Synthesis

Bryan Ackland Department of Electrical and Computer Engineering Stevens Institute of Technology Hoboken, NJ 07030

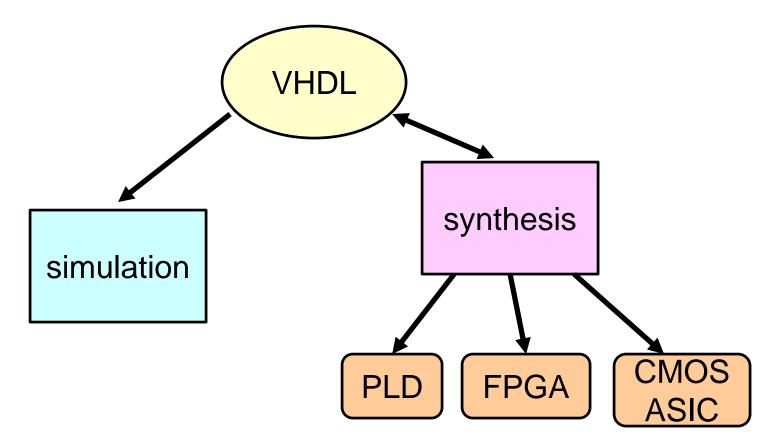

# What is Synthesis?

- Process of creating a RTL or gate level net-list from a VHDL model

- Net-list can be used to create a physical (hardware) implementation

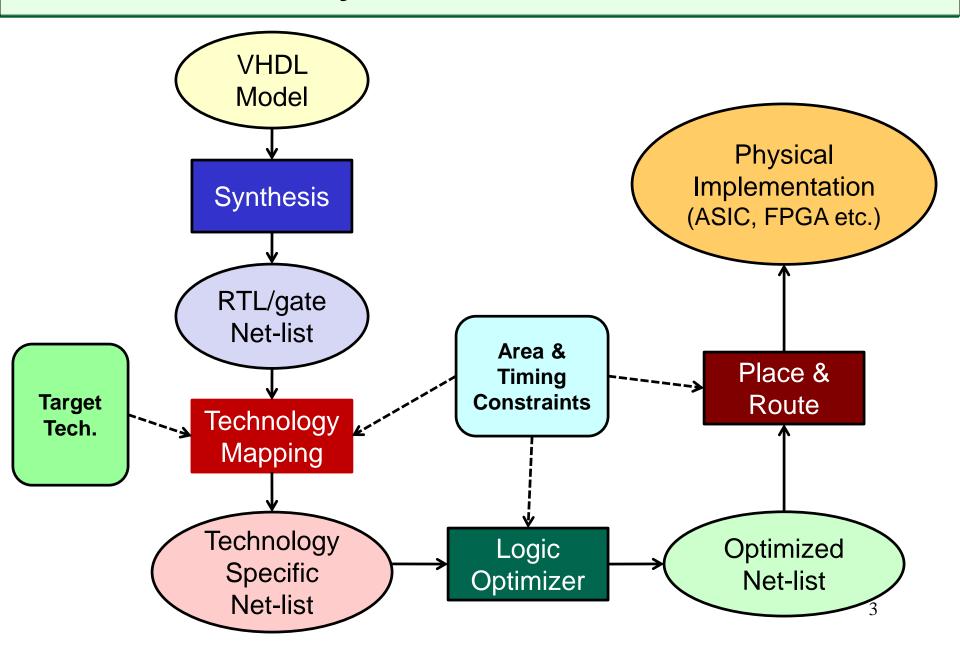

#### **Synthesis Process**

# **Limitations of Synthesis**

- VHDL can model a hardware system at different levels of abstraction from gate level up algorithmic level

- Synthesis tools cannot, in general, map arbitrary high level behavioral models into hardware.

- Many VHDL constructs have no hardware equivalent: wait for 10 ns;

signal a1: real;

y<= x'last\_value;</pre>

```

assert a=b report "mismatch" severity error;

```

- Even if VHDL code is synthesizable, it may lead to very inefficient (in terms of area, speed) implementation

- In moving from VHDL high level behavioral description to synthesizable VHDL hardware description, designer needs to know:

- What subset of VHDL is synthesizable

- What hardware in inferred by various VHDL constructs

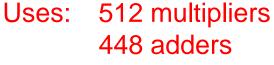

#### **Example of inefficient synthesis**

• 8 x 8 matrix multiply:

```

process (A,B) is

mpr:

variable sum: integer;

begin

for i in 1 to 8 loop

for j in 1 to 8 loop

sum:=0;

for k in 1 to 8 loop

sum := sum + A(i)(k) * B(k)(j);

end loop;

C(i)(j) \leq sum;

end loop;

end loop;

end process;

```

## Inference

- Synthesis is the process of hardware <u>inference</u> followed by <u>optimization</u>

- The synthesis compiler <u>infers</u> hardware structures from your VHDL code

- Those hardware structures are subsequently <u>optimized</u> to meet your area and/or speed constraints.

- Part of being a good synthesis designer is being able to put yourself in the place of the compiler and understand what hardware constructs are likely to be inferred from your code.

# Inferring Hardware from VHDL Code

```

entity synth is

port(A,B,C,D: in integer;

sel: in std_logic_vector(1 downto 0);

Z:out integer);

architecture behavioral of synth is

begin

with sel select

Z <= A+B when "00"

C+D when "10"

0 when others;

end architecture behavioral;</pre>

```

- We need an adder (and a multiplexer).

- How large (how many bits) should the adder be?

- Integers can be up to 32 bits

- What if A,B,C and D are in the range 0-20?

- Do we need two adders, or can one adder be shared?

- Are we more concerned with speed or area?

# **Inferring Signals**

- In regular programming languages, declared variables & constants are used to allocate storage.

- In VHDL, signals are used to represent timed information flow between subsystems.

- How are signals represented in hardware?

- When synthesizing from VHDL, the basic hardware implementations of signals are:

- Wires

- Latches (level sensitive)

- Flip-flops (edge triggered)

- Signals generated by combinational expressions (where signal value depends only on the current value of the inputs) will infer wires

- Signals generated by sequential expressions (where signal value depends on current and previous value of inputs) will infer latches or flip-flops

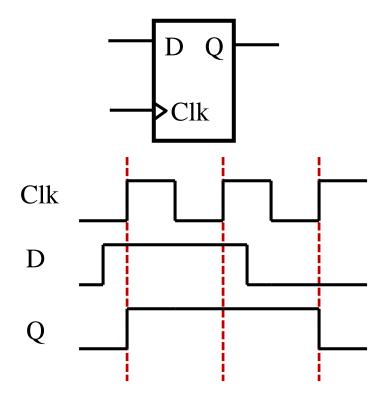

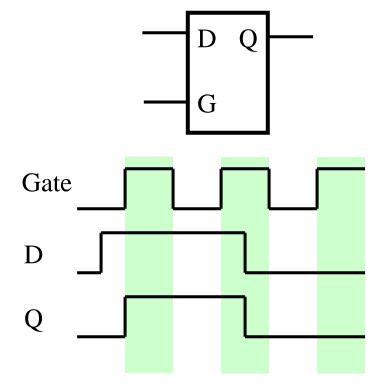

### Flip-flop vs. Latch

#### **Flip-flop**

stores data when clock rises

#### Latch

passes data when G is high stores data when G is low

## **Inference from Declarations**

• When a signal is declared, there needs to be sufficient information to determine the correct number of bits

```

signal result: std_logic_vector (12 downto 0);

signal count: integer;

signal index: integer range 0 to 18:= 0;

```

type state\_type is (state0, state1, state2, state3);

signal next\_state: state\_type;

- How many bits are required to represent *count*?

- Compilers are conservative: they will only perform transformations that are guaranteed not to produce incorrect answers

- Initializations are often ignored

- Need to include run-time initialization in hardware (e.g. reset)

- How many bits are required to represent *next\_state*?

#### Inference from Simple CSA's

*target\_signal <= expression*;

- e.g. A <= (B nand C) or Y after 12 ns;

- A simple CSA assigns a value to a target signal that is a function of the present value of the signals in the RHS expression.

- Whenever an event occurs on any signal in *expression*, target\_signal is re-evaluated.

- no memory of previous values

- The synthesis compiler will infer a combinational circuit

- Delay information (e.g. after 12 ns) will be ignored.

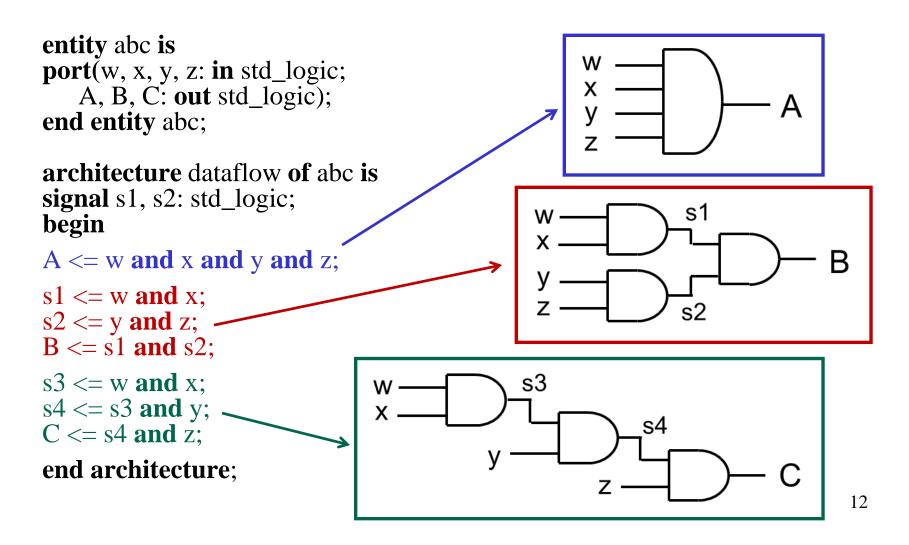

- You can control inferred structure by appropriately grouping logic operations into assignment statements

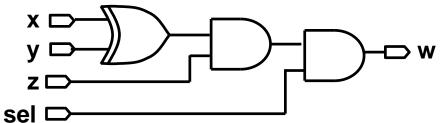

# **Logical Grouping**

• Use of intermediate signals can be used to infer different logical (RTL) implementations:

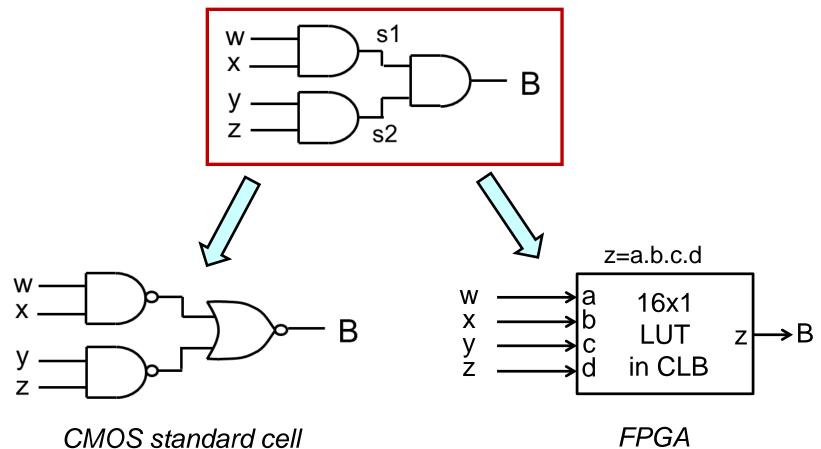

# Logical Grouping Modified by Mapping

RTL structure may be considerably modified by technology mapping and optimization:

implementation

implementation

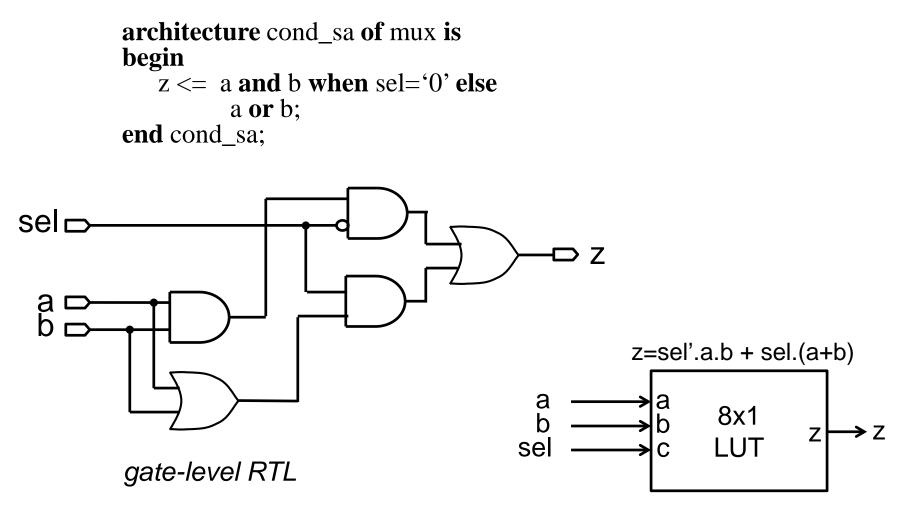

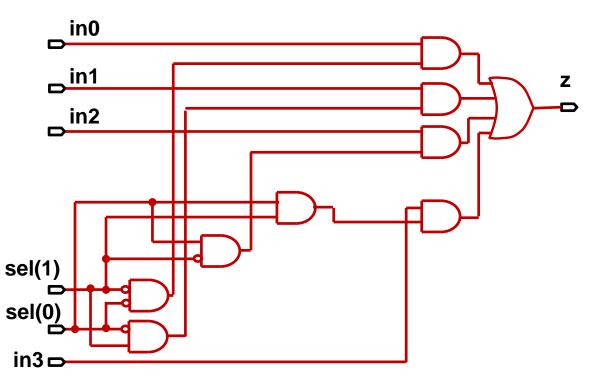

#### **Inference from Conditional Signal Assignment**

FPGA implementation

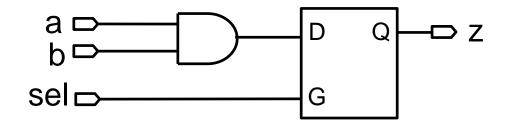

## **Incomplete Assignment Implies Latch**

What happens if there are combinations of inputs that do not result in an assignment?

architecture cond\_sa of mux is begin

z <= a and b when sel='1'; end cond\_sa;

- A latch is inferred to cover the case *sel='0'*

- This is now a sequential circuit is that what we intended?

- We may not care what the result is when *sel='0'*

- Result is unnecessary, hazardous hardware

- If we really wanted sequential operation, better to use flip-flop

- If combinational circuit is intention, make sure output is always assigned a value by using a final else clause

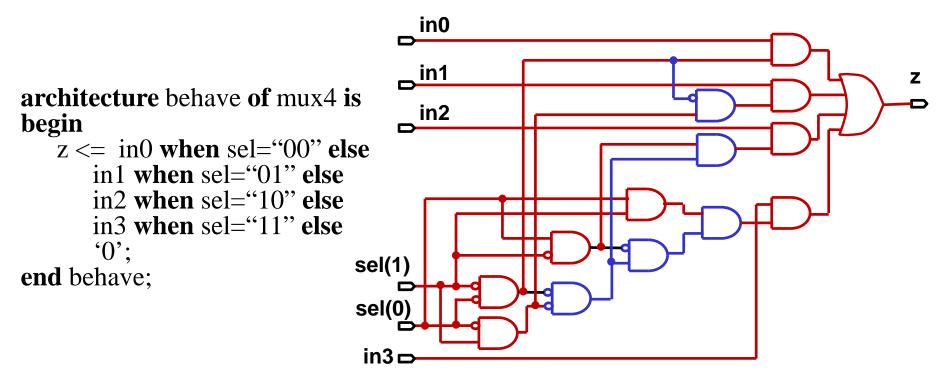

# **Conditional Maintains Priority Order**

• This is great for priority encoder, but what about multiplexer where all conditions are mutually exclusive?

- Only red gates are needed to implement multiplexer

- Blue gates are inferred to maintain priority coding

- Not needed because the clauses are mutually exclusive

## **Selected Signal Assignment**

- SSA is better construct for building a muliplexer

- No longer implied priority order

- Clauses are required to be mutually exclusive

- No redundant gates

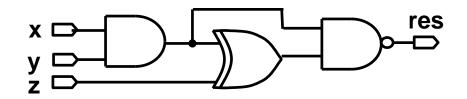

## **Inferring Logic from Processes and Variables**

- Simple variable assignment statements generate combinational logic

- Sensitivity list is usually ignored by synthesis compiler

```

entity syn_y is

port ( x,y,z: in std_logic;

res: out std_logic);

end entity syn_v;

```

```

architecture behav of syn_v is

begin

pr1: process (x,y)

variable v1,v2: std_logic;

begin

v1 := x and y;

v2 := v1 xor z;

res <= v1 nand v2;

end process;

end behav;</pre>

```

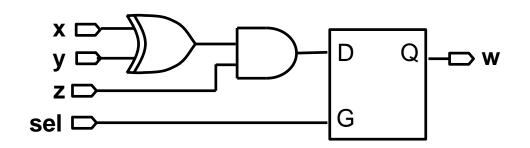

#### **If-then-else Statements**

- Like conditional assignment statements, if-then-else statements will generate latches unless every "output signal" of the statement is assigned a value each time the process executes

- (a) One branch of the if-then-else clause must always be taken AND

- (b) A signal assigned a value in one branch must be assigned a value in all branches.

#### **If-then-else Statements**

```

architecture behav of syn_if is

begin

prl: process (x,y,z,sel)

variable v1: std_logic;

begin

if sel='1' then

v1 := x xor y;

w \ll v1 and z;

p <= V1;

else

w<=0;

end if;

end process;

end behav;

```

## Avoiding latches by "initialization"

- Can ensure that a signal is always assigned in an if-thenelse clause by including a final else clause that assigns a default value to all "output signals" of the statement

- Another alternative is to set a signal to a default value within the process but before the if-then-else statement:

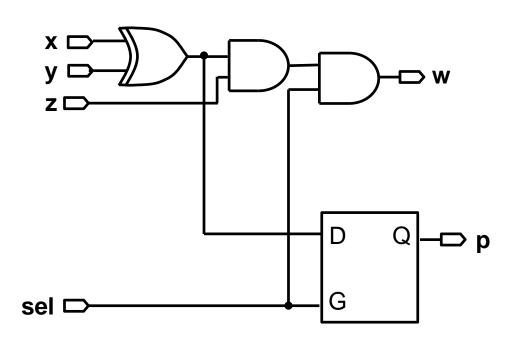

#### **Variables and Inferred Latches**

- Can a variable be used in a manner that implies a latch?

- Yes, if in a single active pass through the process a variable is used before it is assigned:

```

architecture behav2 of syn if is

begin

pr1: process (x,y,z,sel)

variable v1: std_logic;

begin

w <= '0';

if sel='1' then

ХГ

D

Ω

w \ll v1 and z;

V

v1 := x xor y;

end if:

G

end process;

Ζ

end behav2;

sel

```

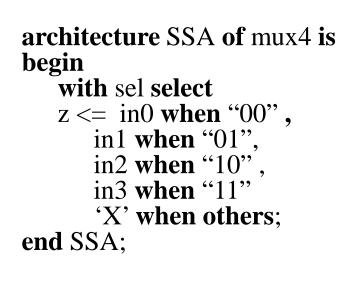

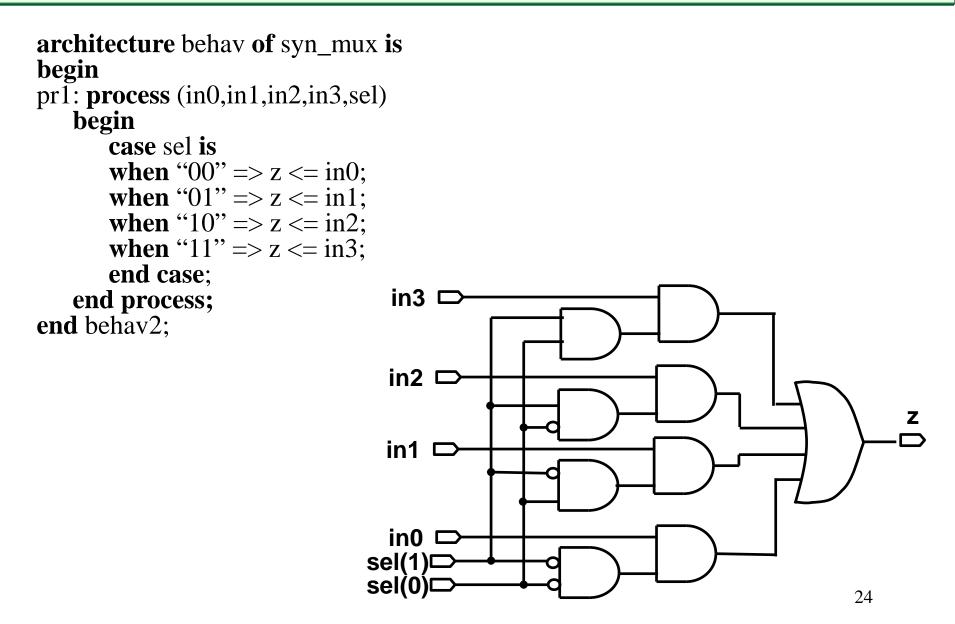

### **Case Statement**

- Case statement is ideally suited for implementing multiplexers

- all clauses must be mutually exclusive

- no implied priority between clauses (unlike if-then-else)

- no redundant logic

- Need to obey same rules to avoid latches

- (a) One branch of the case statement must always be true AND

- (b) If a signal is assigned a value in one branch of a case statement, it must be assigned a value no matter which branch is taken.

#### 4 input multiplexer

# **Sequential Circuits**

- Any moderately complex digital system requires the use of sequential circuits, e.g. to

- identify and modify current state of system

- store and hold data

- identify sequences of inputs

- generate sequences of outputs

- If and case statements and conditional signal assignments can be used to infer latches

- Latches are <u>not</u> preferred means of generating sequential circuits.

- A latch is transparent when LE is high can lead to unintended asynchronous sequential behavior when a result is fed back to an input

- Latches are prone to generate race conditions

- Circuits with latches are difficult to verify timing

- Circuits with latches are difficult to test

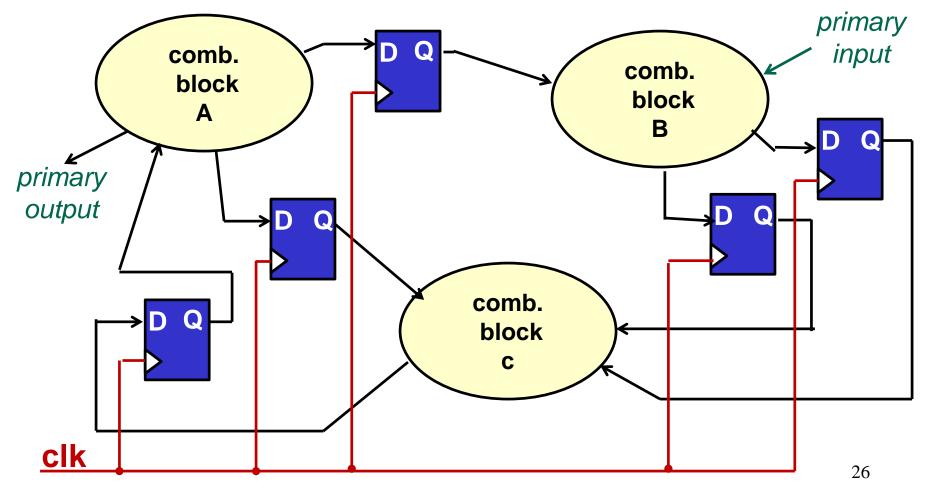

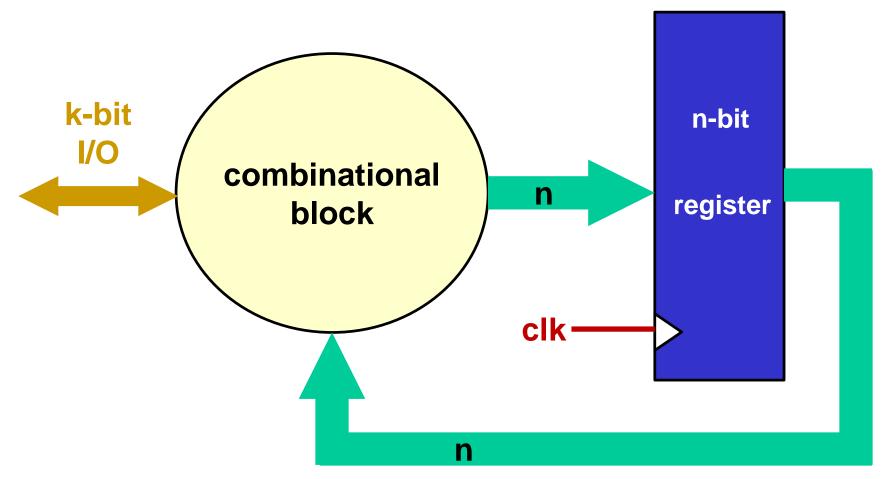

# Synchronous (Single Clock) Digital Design

Preferred design style is combinational circuit modules connected via positive (negative) edge-triggered flip-flops that <u>all use a common clock</u>.

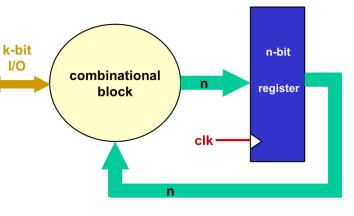

#### **Finite State Machine**

• Single clock synchronous system can be modeled as a single combinational block and a multi-bit register

# Advantages of single clock synchronous

- Edge triggered D flip-flops are never transparent

- no unintended asynchronous sequential circuits

- Timing can be analyzed by:

- determining all combinational delays

- just add them up

- checking flip-flop setup and hold times

- No race conditions

- only time signal values matter is on clock edge

- Easy to test

- Most real systems, however, cannot be designed using a single clock

- different timing constraints on various I/O interfaces

- clock delays across chip

- goal is to make the single clock modules as large as possible<sup>28</sup>

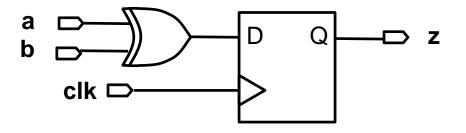

# D Flip-flop

- Edge triggered D flip-flops are preferred sequential component

- Within a process, positive edge triggered operation is inferred using:

if rising\_edge (clk) then -- only with std\_logic type

if clk'event and clk='1' then

• For example:

```

architecture RTL of FFS is

begin

p0: process (a,b,clk)

begin

if rising_edge (clk) then

z <= a xor b;

end if;

end process;

end RTL;</pre>

```

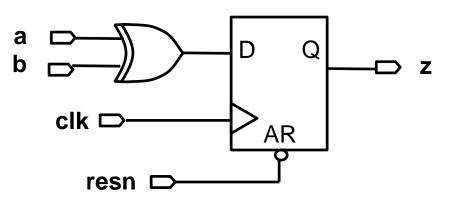

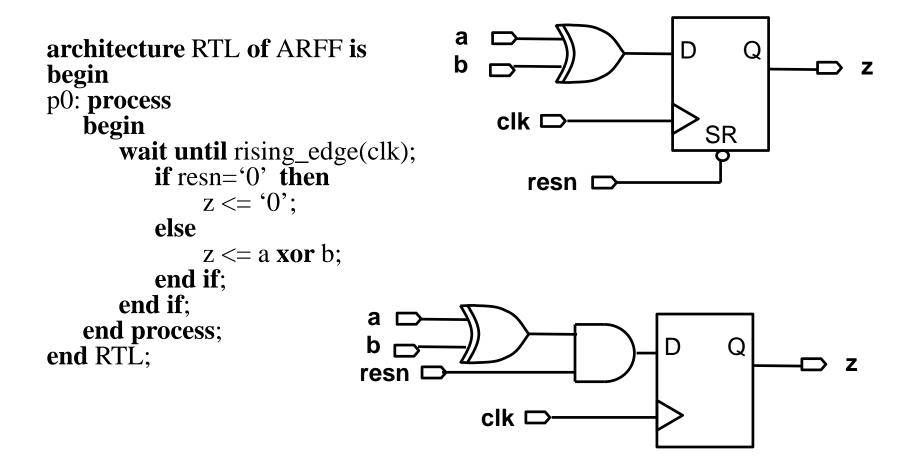

## **Inferring D Flip-flop with Asynchronous Reset**

- Asynchronous reset takes precedence over clock

- Flip-flop can also include asynchronous set

```

architecture RTL of ARFF is

begin

p0: process (a, b, resn, clk)

begin

if resn='0' then

z \le 0';

elsif rising_edge (clk) then

z <= a xor b;

end if;

end process;

end RTL;

```

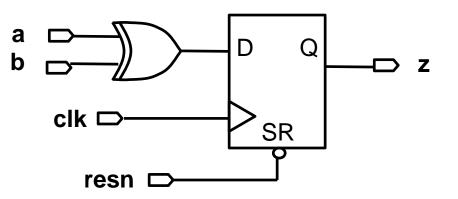

### **Inferring D Flip-flop with Synchronous Reset**

- Synchronous reset waits for clock

- Flip-flop can also include synchronous set

```

architecture RTL of ARFF is

begin

p0: process (a, b, resn, clk)

begin

if rising_edge (clk) then

if resn='0' then

z \le 0';

else

z <= a xor b;

end if;

end if;

end process;

end RTL;

```

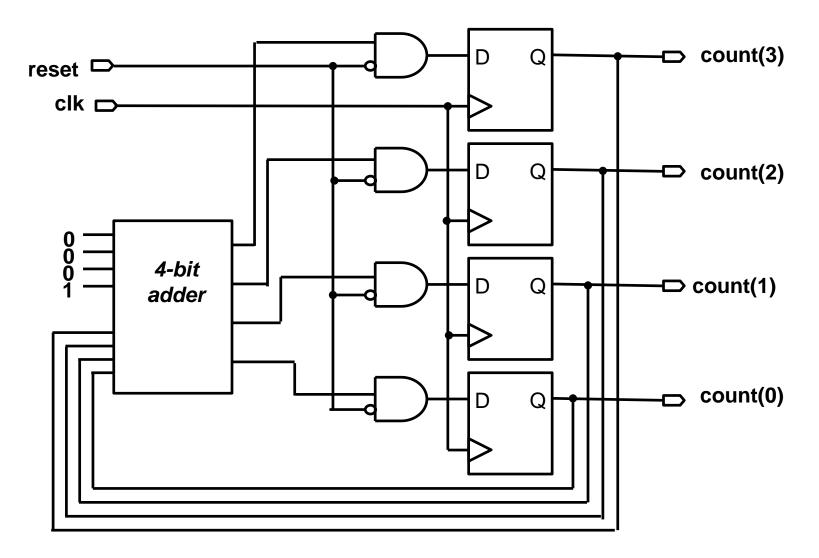

#### **Example: 4-bit synchronous counter**

library IEEE; use IEEE.std\_logic\_1164.all; use IEEE.std\_logic\_unsigned.all;

entity count4 is

port( clk, reset: in std\_logic;

count: out std\_logic\_vector (3 downto 0));

end entity count4;

# architecture RTL of count4 is begin

```

p0: process (clk, reset)

variable vcount: std_logic_vector (3 downto 0);

begin

if rising_edge (clk) then

if reset='1' then

vcount := "0000";

else

vcount := vcount+1;

end if;

end if;

count <= vcount;

end process;

end RTL;</pre>

```

#### **Example: 4-bit synchronous counter**

#### Wait Statement

- Only one wait statement permitted per process

- Must be the first statement in the process

- Must be of the wait until form

- cannot use wait for or wait on constructs

- Either of these will trigger execution on rising clock edge: wait until clk'event and clk='1';

wait until rising\_edge(clk); -- only with std\_logic type

- A D flip-flop will be inferred for <u>all signals assigned in the</u> process

- all signals are synchronously assigned in process

#### **Wait Statement - Example**

- For loop is most commonly supported by synthesis compilers

- Iteration range should be known at compile time

- While statements are usually not supported because iteration range depends on a variable that may be data dependent.

- Compiler will unroll the loop, e.g.:

```

for k in 1 to 3 loop

shift_reg(k) <= shift_reg(k-1);

end loop;</pre>

```

will be replaced by:

shift\_reg(1) <= shift\_reg(0); shift\_reg(2) <= shift\_reg(1); shift\_reg(3) <= shift\_reg(2);</pre>

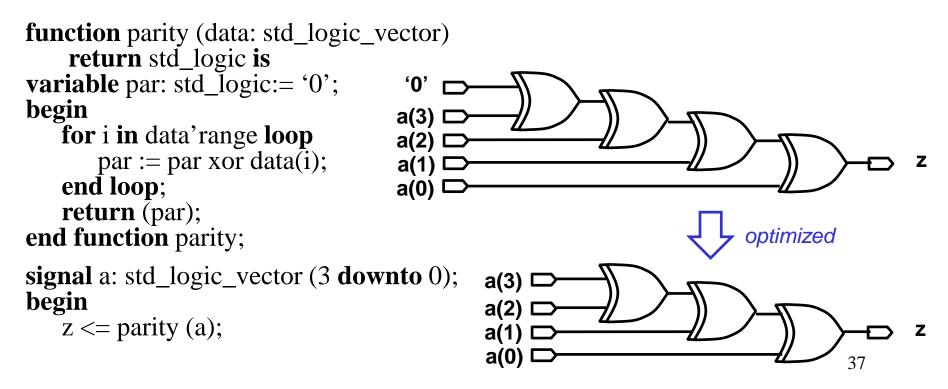

# **Functions**

- Since:

- functions are executed in zero time and

- functions do not remember local variable values between calls

- Functions will typically infer combinational logic

- Function call is essentially replaced by in-line code

#### Procedures

- Like functions, procedures do not remember local variable values between calls

- Procedures, however, do not necessarily execute in zero time

- And procedures may assign new events to signals in parameter list

- Like function, think of procedure calls as substituting the procedure as inline code in the calling process or architecture

- Can include a wait statement, but then cannot be called from a process

- Generally avoid wait statements in a procedure

- Synchronous behavior can be inferred using if-then-else

- If procedure is called from a process with wait statement, flip-flops will be inferred for all signals assigned in procedure

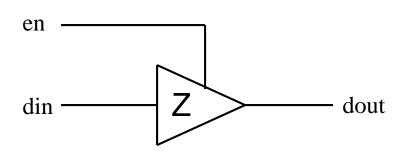

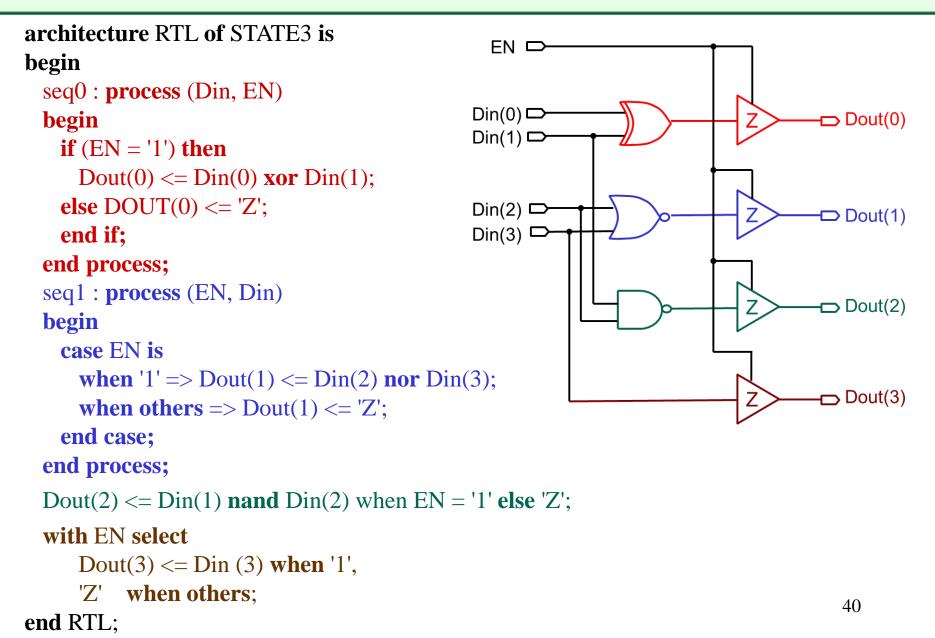

A tri-state gate is inferred if the output value is conditionally set to high impedance Z

| din | en | dout |

|-----|----|------|

| 0   | 1  | 0    |

| 1   | 1  | 1    |

| Х   | 0  | Z    |

#### **Examples of Tri-state Gates**

## **Think of the Hardware Cost**

- Comparison operators like =,>,< require comparator circuits

- Arithmetic operators like +,-, and \* imply adder, subtractor, and multiplier

- Multiplication and division by powers of 2 can be implemented using an arithmetic shift

- Multiplication by simple constants can be accomplished with explicit shift & add (e.g. multiply by 3)

- Order of logic and arithmetic operations:

• Compare the following:

```

architecture RTL of modX is

signal A1, B1: unsigned(15 downto 0);

begin

A1 <= A - 1;

B1 <= B - 1;

seq: process

begin

wait until clk;

case SEL is

when '0' => DOUT <= A1;

when '1' => DOUT <= B1;

end case;

end process;

end RTL;

```

```

architecture RTL of modX is

begin

seq: process

variable v1: unsigned (15 downto 0);

begin

wait until clk;

case SEL is

when '0' => v1:=A;

when '1' => v1:=B;

end case;

DOUT <= v1 - 1;

end process;

end RTL;

```

## **Example: Inferring Synthesis**

• Draw the logic inferred by the following VHDL code:

entity abc is

port (

A,B, clk, reset: IN bit;

C: OUT bit

);

end abc;

architecture RTL of abc is signal W, X, Y, Z; begin  $W \leq X xor Z$ : p0: **process** (clk, A, B, reset) begin X <= '0'; if clk='1' then X <= A:  $Z \ll A$  and B; end if; if reset='0' then Y <= '0'; elsif clk'event and clk='1' then  $Y \leq A \text{ nor } B;$ end if; end process;  $C \ll W$  nand Y; 43 end RTL;

# Summary – Guidelines for Synthesis

- (1) While loop is generally not supported

- (2) All for loops must have statically determined loop ranges

- (3) To avoid a latch being inferred in a conditional CSA, every execution of the statement must assign a value to the target signal

- (4) To avoid a latch being inferred for a signal in a process, every executable path through the process must assign a value to that signal (assign default values before conditionals)

- (5) Using a variable in a process before it is assigned will infer a latch for that variable

- (6) Do not specify initial values for signals

- (7) Include all signals in process sensitivity list to avoid mismatch between pre- and post-synthesis simulation

- (8) All code should infer hardware structure avoid "algorithmic" descriptions of hardware

# Summary – Guidelines for Synthesis

- 9) If possible, specify data ranges explicitly in declarations

- 10) Minimize signal assignment within a process use variables

- 11) If you wish to use both combinational and sequential logic in a process, use if-then statements to infer flip-flops rather than wait statement.

- 12) When possible, move common complex operations out of the branches of conditional code and place them after the conditional code. This will generally lead to less hardware

- 13)Use a case statement rather than if-then-else if clauses are mutually exclusive – avoids redundant priority logic

- 14) Avoid level sensitive latches if they are not part of the target technology library