#### CPE 487: Digital System Design Spring 2018

# Lecture 14 Test Bench Design

Bryan Ackland Department of Electrical and Computer Engineering Stevens Institute of Technology Hoboken, NJ 07030

## **Testing Digital Circuits**

- In our class examples, circuits were limited to a few input & outputs

- Easy to set up test bench with processes to explicitly drive the inputs

- Look at output waveforms to check correct operation

But how do we test this one?

Processor for SONY PlayStation 3

## **Test Vectors**

- For large complex designs, designers will set up a suite of test vectors

- One or more files that contain a sequence of inputs and expected outputs

| inputs           | expected outputs  |

|------------------|-------------------|

| 0010011100000110 | <b>11XX010110</b> |

| 1101001101100101 | <b>11X0111010</b> |

| 0100011010011010 | 1101101110        |

| 1110011111010100 | 0110001110        |

|                  |                   |

- Input vectors are typically applied to circuit under test at some regular clock rate. Outputs are read at same rate and compared to expected outputs

- It can take many millions of vectors to adequately test a complex chip e.g., a microprocessor 3

## **Design Verification vs. Product Testing**

- During the design process, we develop functional test vectors

- Apply vectors similar to what might be expected in normal operation of chip

- Look for correct functionality across broad range of expected inputs

- Purpose of these functional vectors is to debug the design

- Each time design is refined, we reapply the functional vectors to check that no mistake has been made in moving from behavioral modeling to implementation

- Once design has been synthesized into gates, and checked once more using the functional vectors, we develop a new set of manufacturing test vectors

- Now checking for manufacturing defects

## **Testing for Manufacturing Defects**

- Popular approach is to assume that all manufacturing faults can be modeled as a single node being stuck-at either a '0' or a '1'

- Ideally, develop a set of test vectors that would show an error if any node is stuck-at '0' or '1'

- Not practical as it would take too many vectors to exhaustively test for all stuck at faults – tradeoff between test time and cost of sending bad chips into the field

- Ratio of tested faults to all possible faults is known as fault coverage – 90% is considered good for a large, complex chip

Production chip tester.

## **Developing a Functional Test Bench**

- Develop a set of functional test benches using simple example: full adder

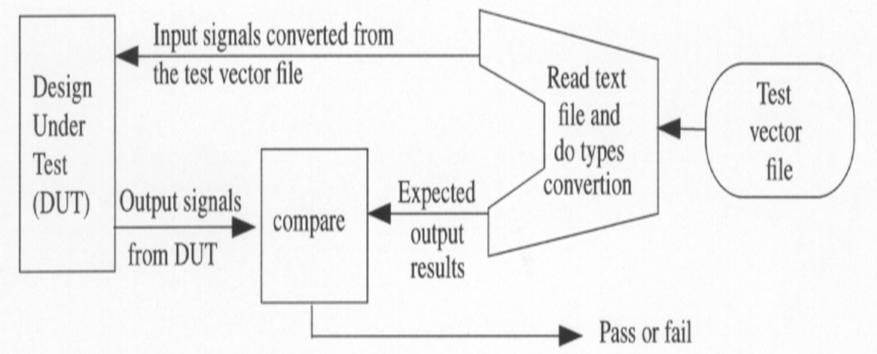

- Move towards fully automated model:

#### **Device Under Test: Full-Adder**

```

library IEEE;

AC

use IEEE.STD LOGIC 1164.ALL;

BD

⊃ sum

cin D

entity fadder is

Port ( A : in STD LOGIC;

⊃ cout

B : in STD LOGIC;

cin : in STD LOGIC;

sum : out STD LOGIC;

cout : out STD LOGIC);

end fadder:

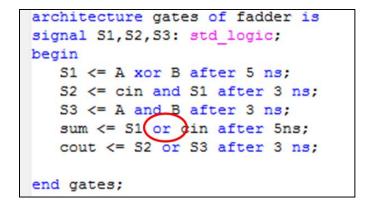

architecture gates of fadder is

signal S1,S2,S3: std logic;

begin

S1 <= A xor B after 5 ns:

S2 <= cin and S1 after 3 ns;

S3 <= A and B after 3 ns:

sum <= S1 xor cin after 5ns;</pre>

cout <= S2 or S3 after 3 ns;

```

end gates;

#### **TB1: A Simple Test Bench**

```

ENTITY fadd tb1 IS

END fadd tb1;

ARCHITECTURE behavior OF fadd tb1 IS

-- Component Declaration for UUT

COMPONENT fadder

PORT (

A : IN std logic;

B : IN std logic;

cin : IN std logic;

sum : OUT std logic;

cout : OUT std logic

);

END COMPONENT:

--Inputs

signal A : std logic := '0';

signal B : std logic := '0';

signal cin : std logic := '0';

--Outputs

signal sum : std logic;

signal cout : std logic;

BEGIN

-- Instantiate the UUT

uut: fadder PORT MAP (

A => A.

B \Rightarrow B,

cin => cin,

sum => sum,

cout => cout

);

```

```

TB: process

constant PERIOD: time:= 20ns;

BEGIN

```

```

A<='0'; B<='0'; cin<='0';

wait for PERIOD;

```

```

A<='0'; B<='1'; cin<='0';

wait for PERIOD;

```

```

A<='1'; B<='0'; cin<='0';

wait for PERIOD;

```

```

A<='1'; B<='1'; cin<='0';

wait for PERIOD;</pre>

```

```

A<='0'; B<='0'; cin<='1';

wait for PERIOD;</pre>

```

```

A<='0'; B<='1'; cin<='1';

wait for PERIOD;

```

```

A<='1'; B<='0'; cin<='1';

wait for PERIOD;</pre>

```

```

A<='1'; B<='1'; cin<='1';

wait for PERIOD;

```

```

wait; -- will wait forever

END process;

END;

```

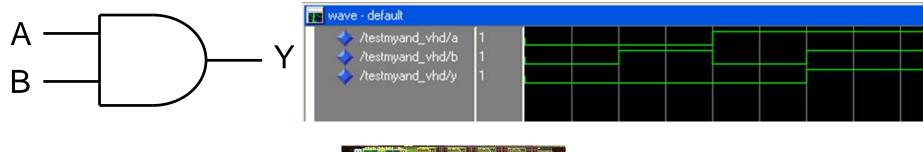

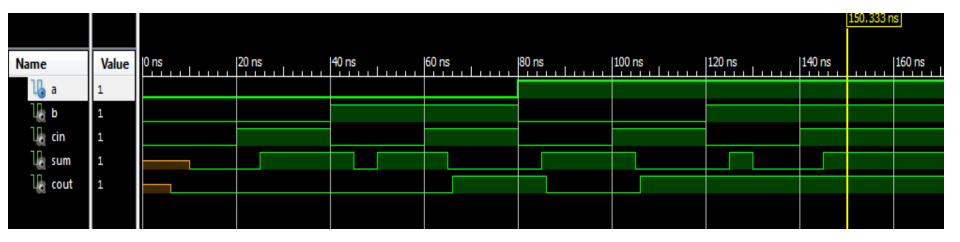

## **TB1: Visually Check Simulation Result**

|        |       | 0.000 ns |       |       |       |       |        |        |        |        |

|--------|-------|----------|-------|-------|-------|-------|--------|--------|--------|--------|

| Name   | Value | 0 ns     | 20 ns | 40 ns | 60 ns | 80 ns | 100 ns | 120 ns | 140 ns | 160 ns |

| Ц_а    | 0     |          |       |       |       |       |        |        |        |        |

| lla b  | 0     |          |       |       |       |       |        |        |        |        |

| 堝 cin  | 0     |          |       |       |       |       |        |        |        |        |

| 퉪 sum  | υ     |          |       |       |       |       |        |        |        |        |

| 퉪 cout | υ     |          |       |       |       |       |        |        |        |        |

|        |       |          |       |       |       |       |        |        |        |        |

|        |       |          |       |       |       |       |        |        |        |        |

This is a Lite version of ISim. Time resolution is 1 ps Simulator is doing circuit initialization process. Finished circuit initialization process. **ISim>**  assert boolean-expression

[report string-expression]

[severity expression];

- The *boolean-expression* is evaluated and if the expression is false, the *string-expression* specified in report statement is displayed in the simulator window

- The severity statement then indicates to the simulator what action should be taken in response to the assertion failure.

- Severity: NOTE, WARNING, ERROR, FAILURE.

#### **TB2: Using Assert Statement**

```

TB: process

constant PERIOD: time:= 20ns;

BEGIN

A<='0'; B<='0'; cin<='0';

wait for PERIOD:

assert(sum='0' and cout='0')

report "Test FAILED" severity error;

A<='0'; B<='1'; cin<='0';

wait for PERIOD;

assert(sum='1' and cout='0')

report "Test FAILED" severity error;

A<='1'; B<='0'; cin<='0';

wait for PERIOD:

assert(sum='1' and cout='0')

report "Test FAILED" severity error;

A<='1'; B<='1'; cin<='0';

wait for PERIOD:

assert(sum='0' and cout='1')

report "Test FAILED" severity error;

```

. .

```

A<='1'; B<='1'; cin<='0';

wait for PERIOD;

assert(sum='0' and cout='1')

report "Test FAILED" severity error;

A<='0'; B<='0'; cin<='1';

wait for PERIOD;

```

report "Test FAILED" severity error;

assert(sum='1' and cout='0')

assert(sum='0' and cout='1')

assert(sum='0' and cout='1')

assert(sum='1' and cout='1')

wait; -- will wait forever

A<='0'; B<='1'; cin<='1';

A<='1'; B<='0'; cin<='1';

A<='1'; B<='1'; cin<='1';

wait for PERIOD:

wait for PERIOD:

wait for PERIOD;

END process;

END;

11

#### **TB2: Using Assert – no errors**

|        |       | 0.000 ns |       |       |       |       |        |        |        |        |

|--------|-------|----------|-------|-------|-------|-------|--------|--------|--------|--------|

| Name   | Value | 0 ns     | 20 ns | 40 ns | 60 ns | 80 ns | 100 ns | 120 ns | 140 ns | 160 ns |

|        | 0     |          |       |       |       |       |        |        |        |        |

|        | 0     |          |       |       |       |       |        |        |        |        |

| -      | 0     |          |       |       |       |       |        |        |        |        |

|        | υ     |          |       |       |       |       |        |        |        |        |

| 堝 cout | υ     |          |       |       |       |       |        |        |        |        |

|        |       |          |       |       |       |       |        |        |        |        |

|        |       |          |       |       |       |       |        |        |        |        |

This is a Lite version of ISim. Time resolution is 1 ps Simulator is doing circuit initialization process. Finished circuit initialization process. **ISim>**

#### **TB2: Using Assert – Introduce error**

```

architecture gates of fadder is

signal S1,S2,S3: std_logic;

begin

S1 <= A xor B after 5 ns;

S2 <= cin and S1 after 3 ns;

S3 <= A and B after 3 ns;

sum <= S1 or din after 5ns;

cout <= S2 or S3 after 3 ns;</pre>

```

Use or instead of xor

end gates;

|        |       | 0.000 ns |       |       |       |       |        |        |        |        |

|--------|-------|----------|-------|-------|-------|-------|--------|--------|--------|--------|

| Name   | Value | 0 ns     | 20 ns | 40 ns | 60 ns | 80 ns | 100 ns | 120 ns | 140 ns | 160 ns |

| Ц_а    | 0     |          |       |       |       |       |        |        |        |        |

| 🗓 b    | 0     |          |       |       |       |       |        |        |        |        |

| 堝 cin  | 0     |          |       |       |       |       |        |        |        |        |

| 堝 sum  | υ     |          |       |       |       |       |        |        |        |        |

| 퉪 cout | υ     |          |       |       |       |       |        |        |        |        |

|        |       |          |       |       |       |       |        |        |        |        |

|        |       |          |       |       |       |       |        |        |        |        |

This is a Lite version of ISim. Time resolution is 1 ps Simulator is doing circuit initialization process. Finished circuit initialization process. at 120 ns: Error: Test FAILED at 140 ns: Error: Test FAILED

ISim>

#### **TB3: Using Test Vector Array**

```

ARCHITECTURE behavior OF fadd tb3 IS

-- Component Declaration for UUT

COMPONENT fadder

PORT (

A,B,cin : IN std logic;

sum, cout : OUT std logic

);

END COMPONENT:

--Inputs

signal A : std logic := '0';

signal B : std logic := '0';

signal cin : std logic := '0';

--Outputs

signal sum : std logic;

signal cout : std logic;

type test array is array(integer range<>)

of std logic vector(0 to 4);

constant test vector: test array(0 to 7):=(

('0', '0', '0', '0', '0'),

('0', '0', '1', '1', '0'),

('0', '1', '0', '1', '0'),

('0', '1', '1', '0', '1'),

('1', '0', '0', '1', '0'),

('1', '0', '1', '0', '1'),

('1', '1', '0', '0', '1'),

('1', '1', '1', '1', '1')

```

```

BEGIN

```

```

testv := test_vector(i);

A <= testv(0);

B <= testv(1);

cin <= testv(2);

wait for PERIOD;

assert (sum=testv(3) and cout=testv(4))

report "Test FAILED" severity error;

end loop;

wait; -- will wait forever

```

```

END process;

```

END:

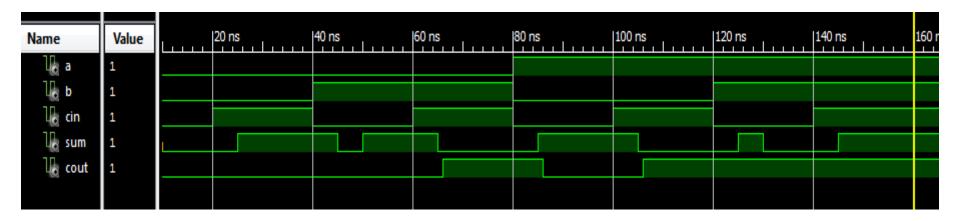

#### **TB3: Using Test Vector Array – no errors**

# run 1000 ns Simulator is doing circuit initialization process. Finished circuit initialization process. ISim>

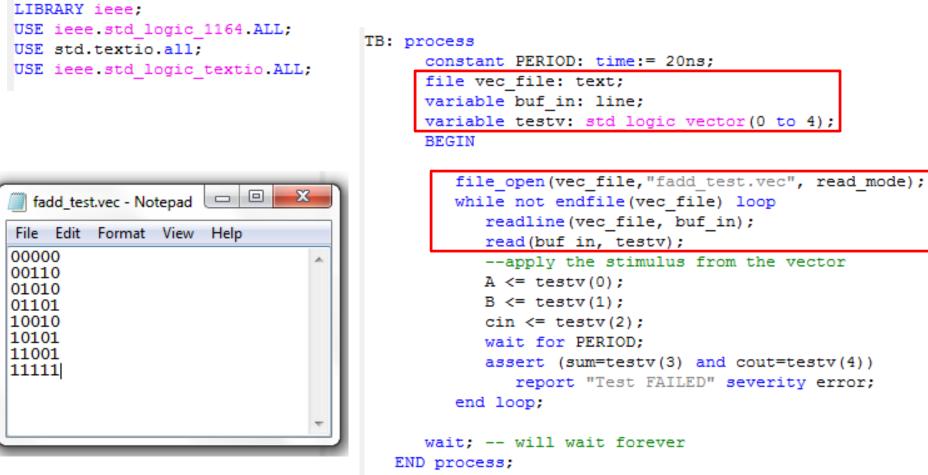

## **Reading and Writing Files – TEXTIO Package**

- A file is a class of object in VHDL (like signal, variable & constant). Each file has a type.

- The standard VHDL library contains the TEXTIO package which provides a set of file types, data types and I/O procedures for simple text I/O to and from files

- To make the package visible:

use std.textio.all;

- TEXTIO read and write procedures are available for predefined types bit, bit\_vector, character and string

- The ieee.std\_logic\_textio package overloads these procedures to support std\_logic and std\_logic\_vector

## **Declaring and Opening Files**

• New Types:

text -- a file of character strings line – a string (to or from a text file)

• Example Declarations

file testfile: text; -- testfile is "file handle"

**variable** L: line; -- L is a single line buffer

• Procedure to open a file:

file\_open(file\_handle, filename, open\_kind);

where open\_kind is one of (read\_mode, write\_mode or append\_mode), for example:

file\_open (testfile, "my\_file.txt", read\_mode);

## **Reading Files**

- readline (*file\_handle*, *line\_buffer*);

- Read one line from "text" file *file\_handle* into *line\_buffer*

- read(*line\_buffer*, *value*);

- Read one item from *line\_buffer* into variable *value*.

- Variable value can be bit, bit\_vector, character or string

- Variable can also be std\_logic or std\_logic vector if IEEE std\_logic\_textio package is used.

- endfile(*file\_handle*); --returns boolean (TRUE if at EOF)

- For example: variable buf\_in: line; variable bit0: std\_logic; begin readline(my\_file, buf\_in);

read(buf\_in, bit0);

18

#### **TB4: Reading Vectors from File**

END;

## **Writing Files**

- writeline (*file\_handle*, *line\_buffer*);

- Write one line to "text" file *file\_handle* from *line\_buffer*

- write(*line\_buffer*, *value*);

- Write variable value into *line\_buffer*

- Variable value can be bit, bit\_vector, character or string

- Variable can also be std\_logic or std\_logic vector if IEEE

std\_logic\_textio package is used.

- For example:

variable buf\_out: line; variable abc : bit\_vector (3 downto 0); begin

```

write(buf_out, "abc is");

write(buf_out, abc);

writeline(my_file, buf_in);

```

#### **TB5: Writing Results to File**

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE std.textio.all;

USE ieee.std_logic_textio.ALL;

ENTITY fadd_tb5 IS

END fadd_tb5;

ARCHITECTURE behavior OF fadd_tb5 IS

-- Component Declaration for UUT

COMPONENT fadder

PORT(

A,B,cin : IN std_logic;

sum,cout : OUT std_logic

);

END COMPONENT;

```

```

--Inputs

signal A : std_logic := '0';

signal B : std_logic := '0';

signal cin : std_logic := '0';

--Outputs

signal sum : std_logic;

signal cout : std_logic;

```

#### BEGIN

```

-- Instantiate the UUT

uut: fadder PORT MAP (

A => A,

B => B,

cin => cin,

sum => sum,

cout => cout

);

```

## **TB5: Writing Results to File (2)**

#### TB: process constant PERIOD: time:= 20ns; file vec file, result file: text; variable buf in, buf out: line; variable testv: std logic vector(0 to 4); BEGIN file open(vec file, "fadd test.vec", read mode); file open(result file, "fadd test.out", write mode); while not endfile(vec file) loop readline(vec file, buf in); read(buf in, testv); --apply the stimulus from the vector $A \ll testv(0);$ $B \leq testv(1);$ cin <= testv(2);wait for PERIOD: assert (sum=testv(3) and cout=testv(4)) report "Test FAILED" severity error; write(buf out, "Time="); write(buf out, now); write(buf out, ":A="); write(buf out, testv(0)); write(buf out, ", B="); write(buf out, testv(1)); write(buf out, ", cin="); write(buf out, testv(2)); write(buf out, " ---> sum="); write(buf out, sum); write(buf out,",cout="); write(buf out,cout); writeline(result file,buf out); end loop; wait: -- will wait forever END process; END:

## **TB5: Writing Results to File (2)**

This is a Lite version of ISim. Time resolution is 1 ps Simulator is doing circuit initialization process. Finished circuit initialization process. **ISim>**

| 🗐 fadd_test.out - Notepad 💷 📼 💌                                                                                                                                                                                                                                                                                                                                                             |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| File Edit Format View Help                                                                                                                                                                                                                                                                                                                                                                  |   |

| <pre>[Time=20 ns:A=0,B=0,cin=0&gt; sum=0,cout=0<br/>Time=40 ns:A=0,B=0,cin=1&gt; sum=1,cout=0<br/>Time=60 ns:A=0,B=1,cin=0&gt; sum=1,cout=0<br/>Time=80 ns:A=0,B=1,cin=1&gt; sum=0,cout=1<br/>Time=100 ns:A=1,B=0,cin=0&gt; sum=1,cout=0<br/>Time=120 ns:A=1,B=0,cin=1&gt; sum=0,cout=1<br/>Time=140 ns:A=1,B=1,cin=0&gt; sum=0,cout=1<br/>Time=160 ns:A=1,B=1,cin=1&gt; sum=1,cout=1</pre> | * |

|                                                                                                                                                                                                                                                                                                                                                                                             | Ŧ |

## **TB5: Writing Results with OR/XOR error**

| Name   | Value | 0 ns | 20 ns | 40 ns | 60 ns | 80 ns | 100 ns | 120 ns | 140 ns | 160 ns |

|--------|-------|------|-------|-------|-------|-------|--------|--------|--------|--------|

| Ц_а    | 1     |      |       |       |       |       |        |        |        |        |

| 🇓 b    | 1     |      |       |       |       |       |        |        |        |        |

| 堝 cin  | 1     |      |       |       |       |       |        |        |        |        |

| 퉪 sum  | 1     |      |       |       |       |       |        |        |        |        |

| 🗓 cout | 1     |      |       |       |       |       |        |        |        |        |

|        |       |      |       |       |       |       |        |        |        |        |

This is a Lite version of ISim. Time resolution is 1 ps Simulator is doing circuit initialization process. Finished circuit initialization process. at 80 ns: Error: Test FAILED at 120 ns: Error: Test FAILED TSim>

| ſ | 📋 fadd_test - Notepad                                                                                                                                                                                                                                                                                                                            | x |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| L | File Edit Format View Help                                                                                                                                                                                                                                                                                                                       |   |

|   | Time=20 ns:A=0,B=0,cin=0> sum=0,cout=0<br>Time=40 ns:A=0,B=0,cin=1> sum=1,cout=0<br>Time=60 ns:A=0,B=1,cin=0> sum=1,cout=0<br>Time=80 ns:A=0,B=1,cin=1> sum=1,cout=1<br>Time=100 ns:A=1,B=0,cin=0> sum=1,cout=0<br>Time=120 ns:A=1,B=0,cin=1> sum=1,cout=1<br>Time=140 ns:A=1,B=1,cin=0> sum=0,cout=1<br>Time=160 ns:A=1,B=1,cin=1> sum=1,cout=1 | * |

| Ļ |                                                                                                                                                                                                                                                                                                                                                  |   |

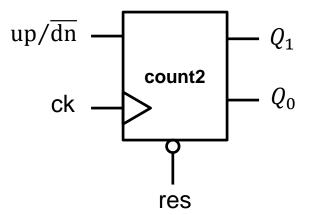

#### **Example: Writing Test Vectors**

• Write a set of test vectors to test the following 2-bit binary counter:

| res | ck | up/dn | Q        |

|-----|----|-------|----------|

| 0   | Х  | Х     | 00       |

| 1   | 1  | 1     | count up |

| 1   | 1  | 0     | count dn |