|

Stevens Software Defined Radio Lab

|

|

Burchard 125

|

|

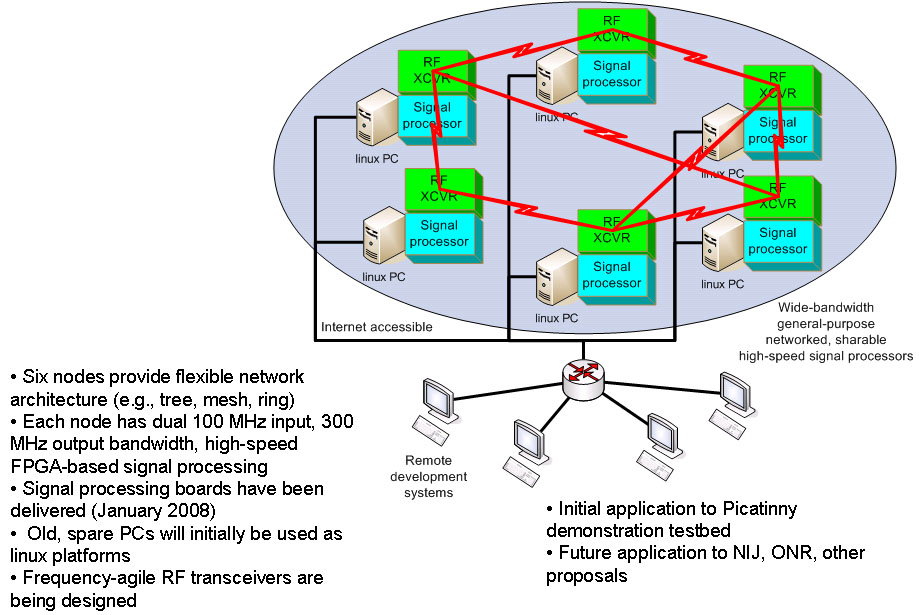

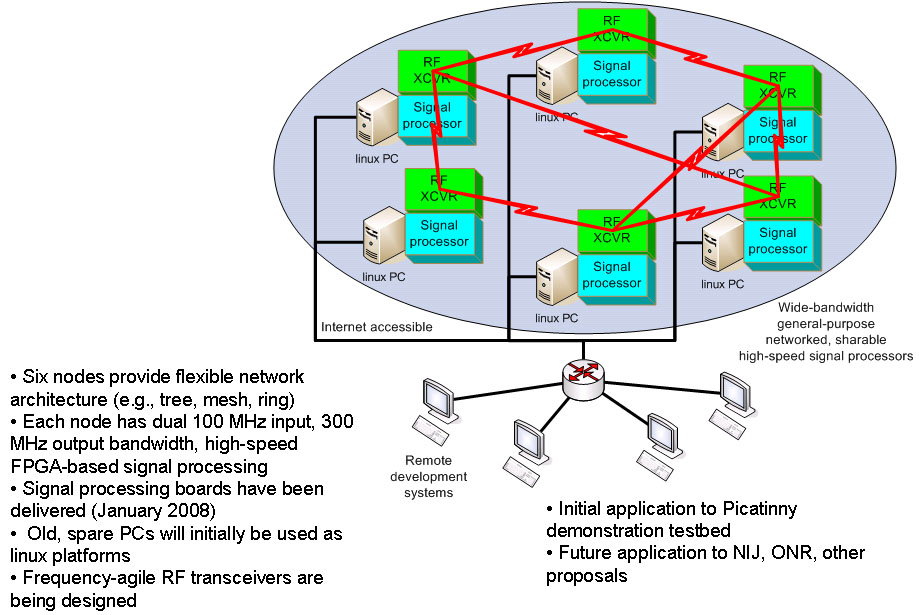

The first hardware instance for the SDR Lab test bed is shown below. With funding from the US Army, we are constructing a wireless testbed to explore several software defined radio concepts.

Our current configuration consists of six nodes, each node being a linux computer as a host, with a Pentek 7640 signal processing board. Each 7640 has two high-speed A/D inputs and two high-speed D/A outputs. For real-time signal processing, each 7640 has a Xilinx Virtex-II Pro XC2VP50 FPGA. Each analog input is capable of operating at a sampling rate of 105 MHz with 14-bit resolution, while each output is capable of operating at a sampling rate up to 500 MHz with 16-bit resolution. The basic signal processing functions (Digital Up Conversion, Digital Down Conversion, and passband tuning) are offloaded from the FPGA with dedicated hardware on the board. With six SDR nodes, we can realize several network architectures (e.g., tree, star, ring or mesh) for reasonable sized systems. In addition, with prior equipment donations by AT&T Labs - Research, we also have RF fading emulators from TAS/Spirent and RF noise generators from Noisecom, allowing a variety of real-world channel conditions to be created. Our first tasks for this lab are getting the signal processing boards operating in a distributed linux environment so they are generally accessible for research purposes. The next major challenge will be to build or buy suitable RF hardware to allow bench-top and over-the-air operation of the systems. |

||

|

||

|

This material is provided for the specific use of students enrolled at Stevens and general research purposes only. Deep linking to this page or subsequent pages is permitted, as long as proper attribution of the source is provided. Electronic or other duplication of this material without prior permission is prohibited. © 2008 Stevens Institute of Technology All rights reserved |

This page was last updated on: